Sunita Chandrasekaran Guido Juckeland Sandra Wienke (Eds.)

# **Accelerator Programming Using Directives**

5th International Workshop, WACCPD 2018 Dallas, TX, USA, November 11–17, 2018 Proceedings

# Lecture Notes in Computer Science 11381

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

# **Editorial Board**

David Hutchison

Lancaster University, Lancaster, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Zurich, Switzerland

John C. Mitchell

Stanford University, Stanford, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

C. Pandu Rangan

Indian Institute of Technology Madras, Chennai, India

Bernhard Steffen

TU Dortmund University, Dortmund, Germany

Demetri Terzopoulos

University of California, Los Angeles, CA, USA

Doug Tygar

University of California, Berkeley, CA, USA

Sunita Chandrasekaran Guido Juckeland · Sandra Wienke (Eds.)

# Accelerator Programming Using Directives

5th International Workshop, WACCPD 2018 Dallas, TX, USA, November 11–17, 2018 Proceedings

Editors

Sunita Chandrasekaran D

Department of Computer and Information

Science

University of Delaware

Newark, DE, USA

Guido Juckeland D Helmholtz-Zentrum Dresden-Rossendorf Dresden, Sachsen, Germany Sandra Wienke RWTH Aachen University

Aachen, Nordrhein-Westfalen, Germany

ISSN 0302-9743 ISSN 1611-3349 (electronic) Lecture Notes in Computer Science ISBN 978-3-030-12273-7 ISBN 978-3-030-12274-4 (eBook) https://doi.org/10.1007/978-3-030-12274-4

Library of Congress Control Number: 2018968279

LNCS Sublibrary: SL2 – Programming and Software Engineering

## © Springer Nature Switzerland AG 2019

This work is subject to copyright. All rights are reserved by the Publisher, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilms or in any other physical way, and transmission or information storage and retrieval, electronic adaptation, computer software, or by similar or dissimilar methodology now known or hereafter developed.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made. The publisher remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

This Springer imprint is published by the registered company Springer Nature Switzerland AG The registered company address is: Gewerbestrasse 11, 6330 Cham, Switzerland

# 2018: 5th Workshop on Accelerator Programming Using Directives (WACCPD)

http://waccpd.org/

Current hardware trends lead to ever more complex compute node architectures offering multiple, heterogeneous levels of massive parallelism. As a result the 'X' in MPI +X demands more focus. A node in a future exascale system is expected to consist of GPU-like accelerators combined with processor architectures of other types. In order to exploit the maximum available parallelism out of such systems, we are in dire need of sophisticated programming approaches that can provide scalable as well as portable solutions without compromising on performance. The expectation from the scientific community is that such solutions should allow programmers to maintain a single code base whenever possible and to avoid requiring maintaining and debugging multiple versions of the same code.

Raising the abstraction of the code is one of the effective methodologies to reduce the burden on the programmer. At the same time such a methodology will require a heroic compiler to be designed. Software abstraction-based programming models such as OpenMP and OpenACC have been serving this purpose over the past several years. These programming models address the 'X' component by providing programmers with high-level directive-based approaches to accelerate and port scientific applications to heterogeneous platforms. Such programming paradigms played a decisive role in establishing heterogeneous node architectures as a valid choice for a multitude of HPC workloads.

The focus of this workshop is to explore this 'X' component in a hybrid MPI +X programming approach. We are looking forward to technical papers discussing innovative high-level language features and their (early prototype) implementations needed to address hierarchical heterogeneous systems, stories and lessons learnt while using directives to migrate scientific legacy code to parallel processors, state-of-the-art compilation and runtime scheduling techniques, techniques to optimize performance, as well as mechanisms to keep communication and synchronization efficient.

WACCPD has been one of the major forums for bringing together users, developers, and the software and tools community to share knowledge and experiences to program emerging complex parallel computing systems.

The WACCPD 2018 workshop received 12 submissions out of which six were accepted to be presented at the workshop and published in the proceedings. The Program Committee of the workshop comprised 26 members spanning university, national laboratories, and industries. Each paper received a maximum of four reviews. Four papers were accepted straight away whereas two papers went through a shepherding phase where the authors were asked to revisit and redo the paper based on feedback obtained from reviewers. The authors were given a 7-day window to revise the paper and resubmit for the shepherd to re-review and decide on an acceptance or a rejection for the workshop.

All the 14 authors were also strongly encouraged to add source files for reproducibility purposes, following SC18 guidelines, upon request from reviewers. Three out of six accepted papers were able to add these source files, which the reviewers greatly appreciated.

The program co-chairs invited Jack Wells from ORNL to give a keynote address on "Experiences in Using Directive-Based Programming for Accelerated Computing Architectures." Dr. Jack Wells is the Director of Science for the Oak Ridge Leadership Computing Facility (OLCF), a DOE Office of Science national user facility, and the Titan supercomputer, located at Oak Ridge National Laboratory (ORNL). Wells is responsible for the scientific outcomes of the OLCF's user programs.

Based on rigorous reviews and ranking scores of all papers reviewed, the following paper won the best paper award. The authors of the best paper award also included reproducibility results to their paper, which the WACCPD workshop organizers had indicated as a criterion to be eligible to compete for the best paper award.

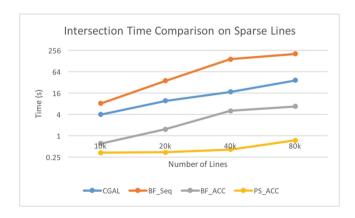

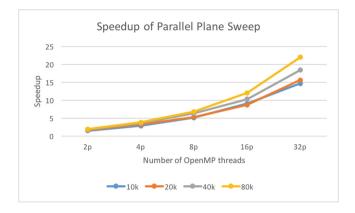

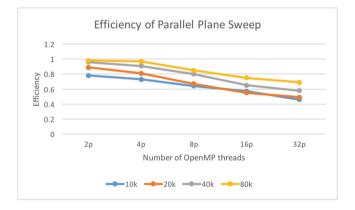

- Anmol Padel and Satish Puri (Marquette University, USA)

- "OpenACC-Based GPU Parallelization of Plane Sweep Algorithm for Geometric Intersection"

Emphasizing the importance of using directives for legacy scientific applications, each presenter was given two recently released textbooks on programming models, one on *Using OpenMP – The Next Step* and the other on *OpenACC for Programmers: Concepts & Strategies*.

January 2019

Sunita Chandrasekaran Guido Juckeland Sandra Wienke

# **Organization**

# **Steering Committee**

Barbara Chapman Stony Brook, USA

Oscar Hernandez ORNL, USA

Michael Klemm Intel, Germany

Kuan-Ching Li Providence University, Taiwan

Satoshi Matsuoka Titech, Japan

Duncan Poole OpenACC, USA

Thomas Schulthess CSCS, Switzerland

Jeffrey Vetter ORNL, USA

# **Program Co-chairs**

Sunita Chandrasekaran University of Delaware, USA

Guido Juckeland HZDR, Germany

Sandra Wienke RWTH Aachen University, Germany

# **Program Committee**

David Berntholdt ORNL, USA James Bever NVIDIA, USA

Sridutt Bhalachandra Argonne National Laboratory, USA

Makus Eisenbach ORNL, USA

Manisha Gajbe Intel, USA

Jeff Hammond Intel Labs, USA

Si Hammond SNL, USA

Christian Iwainsky TU Darmstadt, Germany

Adrian Jackson EPCC, UK Arpith Jacob Google, USA Henri Jin NASA-Ames, USA Gabriele Jost NASA-Ames, USA Jeff Larkin NVIDIA, USA ORNL, USA Seyong Lee Kelvin Li IBM, Canada C. J. Newburn NVIDIA, USA Antonio J. Pena BSC, Spain

Thomas Schwinge Mentor Graphics, Germany

Sameer Shende University of Oregon, USA

Ray Sheppard Indiana University, USA

Scienciae Germany

Peter Steinbach Scionics, Germany

Christian Terboven RWTH Aachen University, Germany

# VIII Organization

Xiaonan Tian Veronica Vergarra Larrea Cheng Wang Michael Wolfe NVIDIA/PGI, USA ORNL, USA Microsoft, USA NVIDIA/PGI, USA

Held in conjunction with

SC18: The International Conference for High-Performance Computing, Networking, Storage and Analysis Dallas, TX November 11–17, 2018

# **Contents**

| Applications                                                                                                                                                                      |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Heterogeneous Programming and Optimization of Gyrokinetic Toroidal Code Using Directives                                                                                          | 3   |

| Using Compiler Directives for Performance Portability in Scientific Computing: Kernels from Molecular Simulation                                                                  | 22  |

| Using OpenMP                                                                                                                                                                      |     |

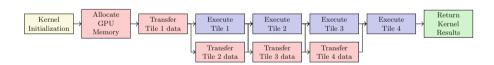

| OpenMP Code Offloading: Splitting GPU Kernels, Pipelining Communication and Computation, and Selecting Better Grid Geometries  Artem Chikin, Tyler Gobran, and José Nelson Amaral | 51  |

| A Case Study for Performance Portability Using OpenMP 4.5                                                                                                                         | 75  |

| Program Evaluation                                                                                                                                                                |     |

| OpenACC Routine Directive Propagation Using Interprocedural Analysis<br>Aniket Shivam and Michael Wolfe                                                                           | 99  |

| OpenACC Based GPU Parallelization of Plane Sweep Algorithm for Geometric Intersection                                                                                             | 114 |

# Heterogeneous Programming and Optimization of Gyrokinetic Toroidal Code Using Directives

Wenlu Zhang<sup>1,2</sup>, Wayne Joubert<sup>3</sup>, Peng Wang<sup>4</sup>, Bei Wang<sup>5</sup>, William Tang<sup>5</sup>, Matthew Niemerg<sup>6</sup>, Lei Shi<sup>1</sup>, Sam Taimourzadeh<sup>1</sup>, Jian Bao<sup>1</sup>, and Zhihong Lin<sup>1(⊠)</sup>

Department of Physics and Astronomy, University of California, Irvine, USA <a href="mailto:rhibongl@uci.edu">rhibongl@uci.edu</a>

Institute of Physics, Chinese Academy of Sciences, Beijing, China

Oak Ridge National Lab, Oak Ridge, TN, USA

NVidia, Santa Clara, USA

Princeton University, Princeton, NJ, USA

BM, New York, USA

**Abstract.** The latest production version of the fusion particle simulation code, Gyrokinetic Toroidal Code (GTC), has been ported to and optimized for the next generation exascale GPU supercomputing platform. Heterogeneous programming using directives has been utilized to balance the continuously implemented physical capabilities and rapidly evolving software/hardware systems. The original code has been refactored to a set of unified functions/calls to enable the acceleration for all the species of particles. Extensive GPU optimization has been performed on GTC to boost the performance of the particle push and shift operations. In order to identify the hotspots, the code was the first benchmarked on up to 8000 nodes of the Titan supercomputer, which shows about 2-3 times overall speedup comparing NVidia M2050 GPUs to Intel Xeon X5670 CPUs. This Phase I optimization was followed by further optimizations in Phase II, where single-node tests show an overall speedup of about 34 times on SummitDev and 7.9 times on Titan. The real physics tests on Summit machine showed impressive scaling properties that reaches roughly 50% efficiency on 928 nodes of Summit. The GPU + CPU speed up from purely CPU is over 20 times, leading to an unprecedented speed.

**Keywords:** Massively parallel computing · Heterogeneous programming · Directives · GPU · OpenACC · Fusion plasma · Particle in cell

## 1 Introduction

Fusion energy would ensure a safe, environmentally friendly, resource conserving power supply for future generations. In an operating fusion reactor, part of the energy generated by fusion itself will serve to maintain the plasma temperature as fuel is introduced. However, to achieve the desired levels of fusion power output, the plasma

<sup>©</sup> Springer Nature Switzerland AG 2019

S. Chandrasekaran et al. (Eds.): WACCPD 2018 Workshop, LNCS

S. Chandrasekaran et al. (Eds.): WACCPD 2018 Workshop, LNCS 11381, pp. 3–21, 2019. https://doi.org/10.1007/978-3-030-12274-4\_1

## W. Zhang et al.

4

in a reactor has to be heated and maintained to its operating temperature of greater than 10 keV (over 100 million degrees Celsius) and additional current drive must be applied. Confinement of such a high density and high temperature burning plasma poses big scientific and technological challenges. One critical mission for the fusion energy research and development is the timely achievement of the capability to understand, predict, control, and mitigate performance-limiting and integrity-threatening instabilities in the burning plasmas. The excitation and evolution of the most important instabilities can be expected to depend on kinetic effects and the nonlinear coupling of multiple physical processes spanning disparate spatial and temporal scales.

In the research of fusion plasma physics, simulations have always been an effective tool due to the complexity of theoretical analysis and the high cost of experiments. After several decades of development in the capability of high performance computing, it becomes feasible to conduct massively parallel simulations to investigate the complex physics using equilibrium and profiles close to realist discharges in fusion devices. Along with the progress in computing power, a set of gyrokinetic theory [1–11] have been proposed and established to construct a set of simple theoretical and numerical model by eliminating the fine-scale gyro-phase dependence through gyro-averaging, which reduces the original phase space dimensionality from six to five. This not only assists in the comprehension of the low frequency physics in magnetized plasmas, such as the anomalous transport that is critical for the magnetic fusion, but also facilitates the development and application of massively parallel simulation codes.

As a well benchmarked massively parallel gyrokinetic toroidal code, GTC [12, 13] is built upon the first-principles and adopts efficient low-noise numerical simulation methods for integrated simulations of key instabilities. This is of great significance since these instabilities not only limit the burning plasma performance but also threaten device integrity in magnetic fusion such as the International Thermonuclear Experimental Reactor (ITER) [14], which is a crucial next step in the quest for the fusion energy. The particle-in-cell method is utilized so that particles are treated with a Lagrangian scheme while fluid moments and field information are calculated with an Eulerian scheme. The capability of GTC has been extensively expanded and verified to deal with a wide range of physical problems such as neoclassical and turbulence transport [15, 16], energetic particle transport by microturbulence [17, 18], Alfven eigenmodes [19-22], radio frequency heating [23], static magnetic island [24] and current-driven instabilities [25, 26]. Over the years, the GTC code has grown to a prominent code being developed by an international collaboration with many users and contributors from the magnetic fusion energy and high performance computing communities.

GTC is the key production code for several multi-institutional U.S. Department of Energy (DOE) Scientific Discovery through Advanced Computing (SciDAC) project and National MCF Energy R&D Program, for example. GTC is currently maintained and developed by an international team of core developers who have the commit privilege and receives contributions through the proxies of core developers from

collaborators worldwide [13]. GTC continuously pushes the frontiers of both physics capabilities and high-performance computing. It is the first fusion code to reach the teraflop in 2001 on the Seaborg computer at NERSC [27] and the petaflop in 2008 on the Jaguar computer at ORNL [16] in production simulations. GTC is also the benchmark and early application code that fully utilizes the computing power of a list of TOP500 machines such as Tianhe-1A [28] and Titan with a CPU and GPU heterogeneous architecture and Tianhe-2 [29] with an Intel Xeon Phi accelerator architecture.

In the pursue of extreme performance from the high computing community, many excellent pioneer works have been carried by computer scientists and developers by porting and optimization the GTC and its companion codes to the GPU on variety of machines. The work of Madduri et al. [30, 31] discussed the porting of an earlier version of GTC to GPU and concluded that the GPU was slower than the CPU for their version of GTC, which only included kinetic ions with adiabatic electrons. Then the GTC GPU [28] version, which was the Tianhe-1A benchmark code developed on the production version using NVidia CUDA libraries, showed some speedup and excellent scaling in the whole machine test with the actual physics simulation parameters. The weak scaling to 3072 nodes of Tianhe-1A was obtained with 2X-3X overall speedup comparing NVidia M2050 GPUs to Intel Xeon X5670 CPUs. A "companion" version of the GTC code, the GTC-P code is a modern, highly portable GTC code now operational on the top 7 supercomputers worldwide [32]. Over the years, GTC-P has been ported and optimized on different supercomputers such as IBM Blue Gene/P (BG/P) at Argonne Leadership Computing Facility (ALCF), IBM Blue Gene/Q (BG/Q) of Mira at ALCF, Sequoia at Lawrence Livermore National Laboratory, the Cray XT4, Cray XE6, and later Cray XC30 at Lawrence Berkeley National Laboratory, et al. [32, 33]. The scalability up to 131,072 BG/P and 32,768 XT4 cores were attained with as little as 512 MB memory per core by incorporating a new radial decomposition method, developed first by Ethier et al. that features a dramatic increase in scalability for the grid work and decrease in the memory footprint of each core [33]. Later, Madduri et al. made further optimizations of the code, such as multi-level particle and grid decompositions, particle binning, and memory-centric optimizations. As a result, they delivered 1.22x, 1.35x, 1.77x, and 1.34x performance improvement on BG/P, the Cray XE6, and Intel Cluster, and a Fermi Cluster, respectively [30]. Recently, the radial domain decomposition was optimized by Wang et al., which enables the GTC-P code scale up to the full capability of Sequoia (98,304 nodes), and Mira (49,152 nodes) [32]. The performance was increased from nearly 50 billion particles per second per step (BPST) to more than 100 BPST on 98,304 Sequoia nodes. GTC-P was also weak scaling to 32,768 Fujitsu K nodes, and about 50 BPST was achieved [34].

In this work, the associated R&D has been focused toward the goal of delivering a comprehensive and modern production version of the fusion GTC code capable of greatly accelerating progress toward a realistic predictive capability for ITER experiments. The technical advances are aimed at providing the computational foundations needed for simulating nonlinear interactions of multiple physical processes covering disparate spatiotemporal scales in burning plasmas. This is part of efforts to develop the

next generation applications for exascale supercomputing platforms. For vast portability and easy maintenance, the directive approach is chosen to lower the technical requirement for students and researchers of fusion plasma physics.

GTC is one of a small but growing number of production applications run on leadership class systems to employ compiler directives to access modern accelerated node hardware. Use of compiler directive programming models such as OpenACC and OpenMP is of increasing importance to achieve performance portability across multiple target computer architectures. We believe the lessons learned in this paper will be useful to other developers wishing to use directives for programming to accelerated architectures.

This paper is organized as follows. Section 2 briefly introduces the benchmark platforms of Titan, SummitDev, and Summit. Section 3 discusses the technical basis of the GTC code, which is followed by the porting and optimization strategies in Sect. 4. Section 5 reports the status of the porting and optimization. Section 6 shows the performance benchmarks. The conclusions are given in Sect. 7.

# 2 Simulation Platforms: Titan, SummitDev, and Summit

All the benchmark runs in the following sections were performed on the Titan, SummitDev, and Summit supercomputers, both hybrid massively parallel processing (MPP) systems with CPUs and GPUs.

The Titan system at Oak Ridge National Laboratory (ORNL) is a Cray XK7 system composed of 200 cabinets containing 18,688 compute nodes, each equipped with a 16-core Advanced Micro Devices AMD Interlagos processor with 32 GB of memory and an NVidia Kepler K20X GPU accelerator with 6 GB memory, with Gemini interconnect. Titan's peak speed is in excess of 27 petaflops. The GPU attains a peak double precision rate of 1.311 TF/s with main memory bandwidth of 250 GB/s and is connected to the CPU by a PCI Express Gen 2.0 bus with an 8 GB/s data transfer rate [41].

SummitDev is an early access system at ORNL used by developers to prepare applications for the 200 PF Summit system to be available in 2018. SummitDev is comprised of 54 IBM Power8 S822LC compute nodes connected with a Mellanox EDR Infiniband network, each node containing two IBM POWER8 processors with 10 cores and 80 hardware threads each. Each CPU is connected by an 80 GB/sec NVLINK connection to two NVidia P100 GPUs with peak double precision rate of 5.312 TF/sec and with 16 GB of on-package high bandwidth memory with peak speed of 732 GB/sec [42].

Summit is the next generation leadership supercomputer at ORNL, which is the 200PF system built upon IBM AC922 architecture. It consists of 4,608 nodes linked with Mellanox EDR 100G InfiniBand network, each node host 2 22-core IBM Power 9 CPUs, 6 Nvidia Volta GPUs, 512 GB DDR4 memory and 96 GB HBM2 memory on GPU.

# 3 Scientific Methods of GTC

As a gyrokinetic particle-in-cell [35, 36] (PIC) code, GTC tracks individual charged marker particles in a Lagrangian frame in a continuous phase-space [10, 11], whereas the moments of particle distribution of different species (thermal ion, thermal electron, fast ion, fast electron, etc.) are simultaneously computed on a stationary Eulerian field mesh. This field mesh is also used to interpolate the local electromagnetic fields at the marker particle positions in phase-space. The trajectories of charged marker particles (guiding centers) in a strong magnetic field are calculated by integrators of the equations of motion in the self-consistent electromagnetic fields computed on the field mesh. The number density and current density carried by each marker particle is then projected to the field mesh through interpolations. The moments of the distributions of species, such as number density, charge density and current density, are then calculated by accumulating the projected quantities of marker particles. The electromagnetic fields are then solved on mesh grids using proper combinations of Poisson equation, Ampere's law, Faraday's law and force-balance equations with finite difference methods [37] and finite element methods [38].

The PIC approach implemented in GTC dramatically reduces the computation complexity from  $O(N^2)$  to  $O(N + M \log M)$ , where N is the number of particles, and M is the number of grid points [34, 39]. The use of spatial grids and the procedure of gyro-averaging reduce the intensity of small-scale fluctuations (particle noise). Particle collisions can be recovered as a "sub-grid" phenomenon via Monte Carlo methods. The system geometry simulated in GTC is a torus with an externally-imposed equilibrium magnetic field [30]. In order to capture and take advantage of the characteristics of this curvature geometry, GTC employs the magnetic flux coordinate system  $(\psi, \theta, \zeta)$  [40], where  $\psi$  is the poloidal magnetic flux,  $\theta$  is the poloidal angle and  $\zeta$  is the toroidal angle. This is the base coordinate used for mesh construction, on which the equilibrium and profiles are built. It is also used to construct an intermediate field-line-following coordinate  $(\psi, \theta, \alpha)$  by a simple transformation  $\alpha = \zeta - q(\psi)\theta$ , where q is the tokamak safety factor (representing magnetic field-line pitch). The introduction of such a fieldline coordinate system makes it convenient to decompose a vector into components parallel and perpendicular to the direction of magnetic field and to separate the rapid guiding center motion along the magnetic field lines from the slow motion across the lines, which promotes the simplicity in theory analysis and efficiency in numerical simulation. In particular, the field-line coordinate system drastically reduced computational complexity in the parallel direction. The Poisson equation can be simplified and solved in the  $(\psi, \theta)$  plane perpendicular to the equilibrium magnetic field in this field-line coordinate system.

Physical quantities and variables in GTC can be divided into various categories. The first one includes the field quantities bounded to the stationary mesh, such as electrostatic potential, vector potential, magnetic fields, and accumulated number density and current density distributions on mesh. Originally, the field solver was built on the Portable, Extensible Toolkit for Scientific Computation (PETSc), which was the best choice in the dual core and multiple code age and has been the major solver for daily electromagnetic simulations. However, it gradually emerges as a serious

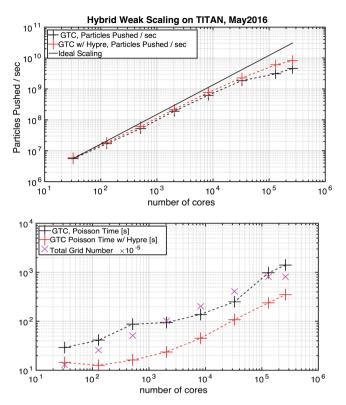

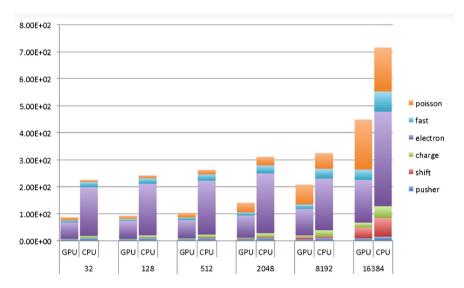

**Fig. 1.** Phase-I weak scaling of GTC on Titan (top), with the number of nodes ranging from 32 to 16384 (88% of the whole machine). Both grid number and total particle number are increased, but the number of particles per core remains constant. The Poisson time (bottom) shows the improved performance due to the Hypre multigrid solver. The total grid number is also shown.

performance hot spot later in the many-core and heterogeneous architecture era due to its lack of in-node accelerations for many-core architectures, for instance for general purpose GPU and Intel Xeon Phi.

The other category includes marker particle related quantities for every species, such as physical position, velocity or momentum, particle number and electric current carried by each marker particle. Depending on the physics studied, a typical production run in fusion plasma research may have multiple species with different governing equations, such as thermal ions, thermal electrons, energetic ions, energetic electrons, impurities, etc. Originally, each species had its own set of functions and subroutines which are used to calculate the particle trajectories (push subroutine), manage and exchange particle information between computing devices and processes (shift subroutine), and aggregate number density and current density as well as the thermal pressure carried by each particle (charge subroutine).

GTC has successfully transferred the physical models into computing power by employing a multi-level palatalization technique, which utilizes the Message Passing Interface (MPI) to manage and balance the distributed computing resources cross

computing nodes or devices on the top level, and utilizes shared memory multiprocessing (SMP) techniques via OpenMP and OpenACC/CUDA inside each node or device on the lower level so that it can take the advantage of the hardware hierarchy of modern massively parallel computers and reach a scale up to millions of conventional CPU cores and heterogeneous accelerating devices such as NVidia GPU and Intel Xeon Phi (MIC) chips.

# 4 Porting and Optimization Strategy

When porting the GTC code to the next generation supercomputing machines powered by accelerators or co-processors such as the GPU or Intel Xeon Phi (MIC), significant challenges are anticipated. Achieving high parallel efficiency on complex modern architectures is in general a formidable task facing PIC codes because of potential fine-grained data hazards, irregular data access, and low arithmetic intensity. Attaining high performance becomes an increasingly complex challenge as HPC technology evolves towards vast on-node parallelism in modern multi- and many-core designs. In order to harness the computing power of advanced systems such as Summit, application codes, including GTC, need to be carefully designed such that the hierarchy of parallelism provided by the hardware is fully utilized. To this end, the multithreading capabilities in the GTC code will be enhanced.

GTC was originally written in Fortran 90. The current GTC version has four species of particles: thermal ions, fast ions, fast electrons and kinetic thermal electrons. Many routines are shared between those particle types. In fusion simulations using GTC, the number of particles per mesh cell varies from tens to thousands in a typical production run for each particle species, which means that every cell would have O (10)–O(10³) of particles. In other words, the total number of particles is O(10)–O(10³) larger than the total number of cells (with field data on cells). Most of the data, either on disk or in memory, and runtime—including I/O time and computing time—are accordingly consumed by the particle routines instead of field routines, which has been consistent with our benchmarking results.

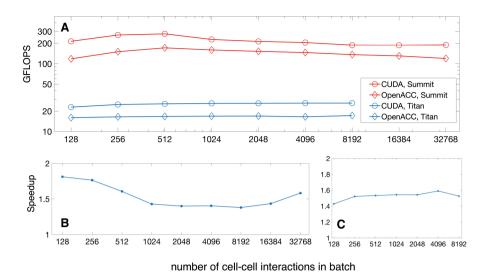

The preceding analysis and observations suggest that particle related routines are the key for optimizing the PIC code like GTC. An appropriate effective strategy for porting GTC to a CPU-GPU heterogeneous architecture would be as follows: migrate all particle relevant data and computing onto the GPU. This approach will not only enable the utilization of the most powerful computing unit of the heterogeneous architecture but also minimize the data transfer between the CPU and the GPU which can be the most challenge part when utilizing GPU in high performance computing. Instead of porting each particle species one by one, all the particle related routines are replaced with a set of unified push, charge and shift routines, which can then be ported to the GPU using OpenACC. After the successful port of particle related part, the field solvers will also be ported onto the GPU to boost the computing performance of field solvers (Figs. 1 and 2).

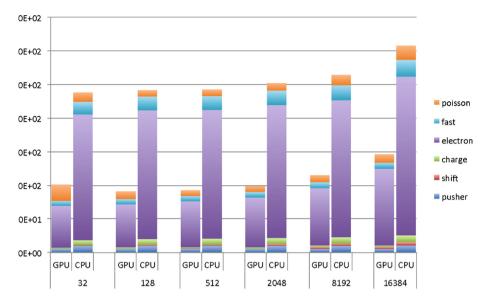

**Fig. 2.** The Phase I timing breakdown for GTC particle weak scaling study on Titan. Note: x-axis is the number of nodes and y-axis the total wall-clock time. The GPU delivers up to 3.0X speedup compared with the CPU.

Given the existing MPI-OpenMP framework, the most natural parallel framework for GTC on CPU-GPU nodes would be using one MPI rank per GPU. Since the CPU version is already parallelized using OpenMP, OpenMP threads should also be enabled to utilize all the available CPU cores.

A large part of the performance optimization work will thus focus on multithreading for NVidia GPU and Intel Xeon Phi architectures (MIC), as well as current multicore processors. Fortunately, the GTC code has been using multithreading for more than a decade and has already had initial porting efforts to advanced heterogeneous architecture systems that deploy the GPU and Intel MIC.

To satisfy the needs for performance portability across multiple HPC system architectures, GTC will initially support multiple programming models via conditional compilation. For shared memory multi-core and Intel Xeon Phi many-core processors, OpenMP parallel directives are used. Support for NVidia GPUs will be deployed using OpenACC directives. An alternative conditionally compiled CUDA code path will be available for cases when compilers are not yet able to generate well-performing code for OpenACC. Later as compiler support becomes available, OpenMP 4.5 and 5.0 target directives will be evaluated as a potential performance portability solution.

GTC currently uses the DOE-funded PETSc toolkit to implement the electromagnetic parallel solvers. PETSc is a well-established MPI-based framework through which many different solvers can be exercised without having to change the source code. Advanced third-party packages, such as LLNL's Hypre multigrid solver, can also be used via the PETSc framework with a simple parameter change in a runtime configuration file. Nevertheless, in spite of its successful use in GTC, PETSc has some

limitations with respect to today's advanced computer architectures. The main draw-back is its lack of multithreading support, which especially impacts global PIC codes like GTC since they run routinely in mixed-mode MPI + OpenMP. It would clearly be beneficial to introduce OpenMP multithreading at the lowest level, for example, in the PETSc functions. This would help us avoid having to deal with non-thread-safe issues in higher-level functions.

In order to identify the hotspots and performance issues, code profiling was performed to reveal performance characteristics and to identify performance issues. The code's timer instrumentation for major parts of the computation was revised to provide performance data needed for the project (Fig. 3).

**Fig. 3.** The Phase I timing breakdown for GTC hybrid weak scaling study on Titan. Here the work per processor is increased as node count is increased. Note: x-axis is the number of nodes and y-axis the total wall-clock time. GPU delivers up to 3.0x speedup compared with CPU.

# 5 GPU Porting Status

Baseline code versions were extracted from current production version of GTC (Fortran) as a starting point of the code porting and optimization work. Firstly, all the particle routines (push, charge and shift) for thermal ions, fast ions and fast electrons and kinetic thermal electrons have been replaced by the set of unified routines, which can operate on every species controlled by the calling parameters like:

push(species\_name, and other parameters)

charge(species\_name)

shift(species\_name)

where species\_name is the description keyword which can be any of "thermal-ion", "thermal-electron", "fast-ion" or "fast-electron". Such species, including both the thermal and fast particles, are described by diverse physical models such as fully-kinetic, gyrokinetic, drift-kinetic, or fluid-kinetic hybrid. This makes it possible that all species benefit from optimizations, for example OpenACC optimizations for the GPU, through changing only one subroutine.

**Table 1.** Phase II GPU and CPU timings (in seconds) from the preliminary SummitDev benchmarks. For comparison, the same physics case, for both GPU and CPU, is shown for Titan. All runs use 32 MPI ranks; GPU runs have 1 GPU/MPI rank; the SummitDev CPU run has 5 OMP/MPI rank; and the Titan CPU case has 8 OMP/MPI rank, however in the data shown here, we assume an ideal scaling in OMP from 8 to 16 threads, and so the data here is the real time divided by 2. This latter point is done to yield a lower bound in the possible speed up. Also, so as to keep the GPU to MPI rank ratio unity, there are 2 ranks/CPU and 1 rank/CPU on SummitDev and Titan, respectively; hence, SummitDev CPUs have a larger compute load.

|           | SummitDev | SummitDev | Titan   | SummitDev | Titan CPU      |  |

|-----------|-----------|-----------|---------|-----------|----------------|--|

|           | GPU       | GPU       | GPU     | CPU       | w/PETSc (Ideal |  |

|           | w/AmgX    | w/PETSc   | w/PETSc | w/PETSc   | OMP)           |  |

| Pushi     | 0.66      | 0.65      | 2.37    | 23.97     | 17.3           |  |

| Shifti    | 0.26      | 0.26      | 0.61    | 21.07     | 7.8            |  |

| Chargei   | 0.66      | 0.65      | 1.03    | 9.59      | 2.0            |  |

| Electron  | 8.40      | 8.37      | 22.40   | 370.23    | 266.0          |  |

| Fast      | 1.53      | 1.54      | 4.74    | 55.47     | 28.7           |  |

| Poisson   | 2.64      | 14.67     | 10.19   | 9.54      | 8.1            |  |

| Pushfield | 0.27      | 0.27      | 0.53    | 0.26      | 1.0            |  |

| Total     | 14.42     | 26.41     | 41.87   | 490.13    | 330.9          |  |

Secondly, these unified routines have been successfully ported to the GPU using OpenACC directives supported by PGI compiler. GTC's main data structure is allocatable arrays within modules. The "acc declare" directive was used in the module file to specify all the arrays that the GPU needs to access. Then, the CPU code for allocating the array typically will not require any change since the OpenACC runtime will automatically allocate a GPU copy if an array is specified in "acc declare". Whenever data needs to be copied between the CPU and the GPU, the "acc update" directive was used. Finally, the "acc host\_data" directive was used to interoperate with the CUDA kernels.

The unified push routine was ported to the GPU using OpenACC. Most of the push time is spent in two loops. The first loop performs a gather operation from grid points to particles. By porting this loop to CUDA, it was identified that using texture cache for the grid arrays will lead to  $\sim 3X$  speedup compared to the base OpenACC version. So, enabling texture cache in OpenACC will be an important next step for optimizing this loop. The second loop updates the particle locations. It was identified that the memory access of the private array "dx" was the main bottleneck. This "dx" array stores the coefficients used to interpolate the local field quantities from the Euclidian meshes.

The optimization was to move the array bound variable for dx to a module file as a parameter and rewrite some of the loops involving dx using the array bound parameter. Those changes enabled the compiler to put this array in local memory, which led to  $\sim 4 \mathrm{X}$  speedup compared to the base OpenACC version. So, this made a case for adding texture cache support to OpenACC. Experimental support of texture cache is now being added to PGI's OpenACC compiler, and we will test it when available.

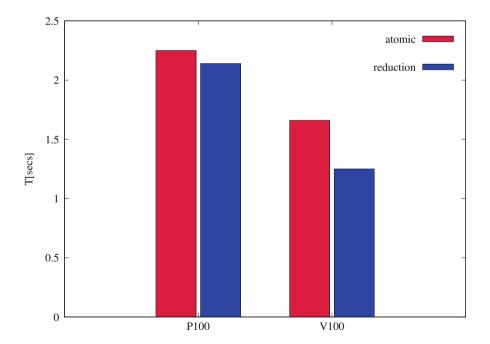

The unified charge routine was ported to the GPU using OpenACC. Because different particles may write to the same grid points, the OpenACC atomic directive was used to handle write collisions. This strategy looked to be working well.

The shift routine was ported to CUDA before the US DOE Center for Accelerated Application Readiness (CAAR) program. Since shift routine is not modified by developer often at all, the GTC team thinks it's fine to use the CUDA version for this routine. So, the CUDA port in previous version was used for shift routine.

A binning subroutine, based on the out-of-place counting sort algorithm, was implemented in GTC (radial\_bin.F90). The first version of the binning algorithm bins all particle species in the radial dimension periodically to improve data locality for charge deposition and field interpolation. For linear problems, where spatial change is small in the radial dimension from one time step to the next, up to 10% overall speedup is observed. It is expected that binning will speed up the performance significantly for nonlinear problems. Later, a cell-based binning was developed and improved the performance by 70% for electron subroutines. Overall, over 10% performance improvement is observed by enabling the cell-based binning.

Both Array of Structure (AoS) and Structure of Array (SoA) data layouts for particles have been implemented on a simplified version of GTC. For GPU, performance analysis is conducted using CUDA profiling toolkit nvprof on a single Titan node. Higher bandwidth and transactions are observed for the AoS layout. Overall no significant speedup is obtained with the SoA data structure for all versions including CPU, GPU (OpenACC) and GPU (CUDA) of the code. We thus decide to use AoS layout for all particle species (as before). The SoA alternative will be available in the future for architectures for which this data layout might improve performance.

Due to increasing relative costs of the Poisson field solve, the PETSc standard solver has been replaced with several alternatives. The Hypre algebraic multigrid solver, whether used standalone or as part of PETSc, runs up to 11X faster than the PETSc standard solver on SummitDev. An early GPU-enabled version of Hypre gave up to 15X improvement over PETSc, and furthermore the NVidia AmgX solver executed up to 27X faster than PETSc. The new solvers also scale much better than PETSc, an increasingly important property as larger and more complex problems are attempted.

GTC uses explicit OpenACC directives to manage GPU data. Unified memory has been introduced since CUDA 6.0 for reducing the complexity of GPU programming and improving performance through data locality. Though typical unified memory implementation has lower performance than explicit memory management, it is interesting to port GTC to unified memory to evaluate the tradeoff between productivity and performance. The initial experiments have suggested that using unified memory in GTC incurred a significant performance penalty due to page fault of Fortran automatic arrays. It is expected that the performance of the unified memory will be improved as PGI provides optimized pool allocator.

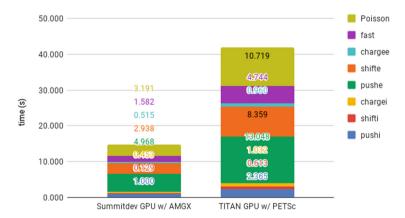

**Table 2.** Phase II GPU speedups, for 15 time steps. SummitDev speedups are relative to the SummitDev CPU w/PETSc & 5 OMP thread/rank case. The Titan GPU speedup is relative to the Titan CPU w/PETSc & Ideal OMP case (see Table 1 caption). All GPU runs use 32 MPI, with 1 GPU/rank.

|           | SummitDev GPU    | SummitDev GPU     | Titan GPU         |

|-----------|------------------|-------------------|-------------------|

|           | w/AmgX, Speed up | w/PETSc, Speed up | w/PETSc, Speed up |

| Pushi     | 36.2             | 36.6              | 7.3               |

| Shifti    | 82.5             | 80.5              | 12.7              |

| Chargei   | 14.6             | 14.7              | 1.9               |

| Pushe     | 27.4             | 27.6              | 14.0              |

| Shifte    | 76.1             | 75.9              | 9.6               |

| Chargee   | 10.2             | 10.2              | 2.7               |

| Fast      | 36.2             | 36.0              | 6.0               |

| Poisson   | 3.6              | 0.7               | 0.8               |

| Pushfield | 1.0              | 1.0               | 1.8               |

| Total     | 34.0             | 18.6              | 7.9               |

## 6 Performance

A set of test problems was developed for evaluating performance (see scaling studies below). The physics case [21] in the 2013 Physical Review Letters by Wang et al. was prepared as a base case to measure improvements in performance. This choice is appropriate since it is a good representation of future production runs and GTC's capabilities, since it employs all particle species, electromagnetic capabilities, experimental profiles and realistic tokamak equilibrium.

# **6.1** Solver Performance Improvement

The GTC Poisson solver currently runs on the CPU. Though it is presently not the most time-consuming part of GTC simulations, the solver time requirements have become more significant since other parts of the code have been accelerated using GPUs. We have replaced the standard PETSc solver with a Hypre multigrid solver. This solver is threaded to effectively use the CPUs and is also scalable to many compute nodes. Figure 1 shows comparative timings of the PETSc solver and the Hypre multigrid solver for a representative set of GTC test cases. The Hypre solver for these cases is  $\sim 4X$  faster than the standard PETSc solver and has better scaling properties.

# **6.2** Scaling Performance

Two sets of weak scaling studies were carried out on Titan up to nearly the full system (16,384 nodes; at the time of this study, many Titan nodes were unavailable, making it impossible to run on all 18,688 nodes). The first test set is called "particle weak scaling study", where we fix the grid size, but scale the total number of particles. The second set of tests is called "hybrid weak scaling study", where we scale both the grid size and total number of particles. The first study holds the number of particles per MPI rank and the number of grid cells per MPI rank nearly constant, thus reflecting a conventional weak

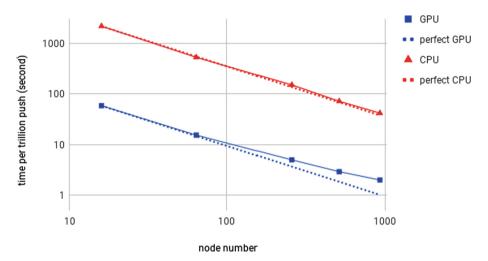

scaling study; the second study is a more realistic scaling study based on typical production run of the code: grid size is proportional to the square root of number of nodes. For both sets of weak scaling study, the number of particles per processor is fixed at 3.2 million. Compared with CPU (16 cores AMD 6274), GPU (NVidia K20x) has boosted the overall performance by 1.6–3.0X. The decrease of the performance speedup in large processor counts is mainly due to the increased portion of the non-GPU accelerated subroutines as well as MPI time. These tests were conducted in May 2016 (Fig. 4).

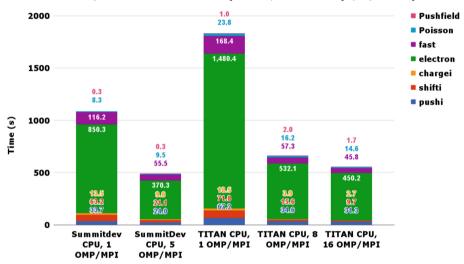

#### GTC SummitDev / TITAN CPU Benchmark (32 MPI, 15 Time Steps, w/ PETSc)

#### GTC SummitDev / TITAN GPU Benchmark (32 MPI, 32 GPU, 15 time steps)

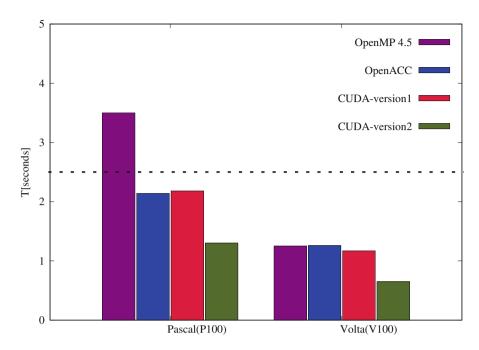

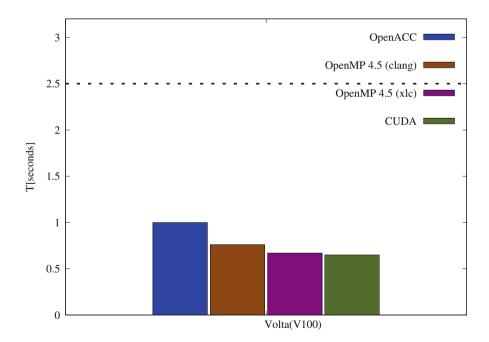

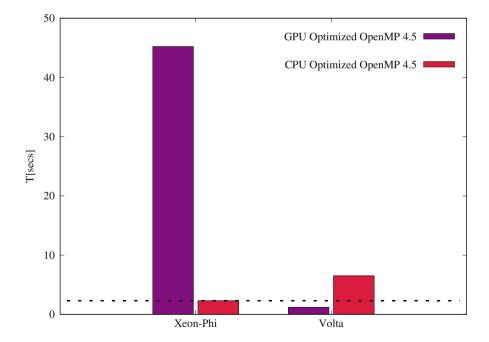

**Fig. 4.** The Phase II timing breakdown for GTC performance study on SummitDev and Titan for 15 time steps and 32 MPI processes. Note that in order to keep the GPU to MPI ratio unity, there are 2 ranks/CPU and 1 rank/CPU on SummitDev and Titan, respectively. Hence, SummitDev CPUs have a larger load. (Top) Pure CPU tests with a scan of OMP thread/rank. (Bottom) GPU tests. All GPU runs use 1 GPU/rank.

#### 6.3 Tests on SummitDev

To foreshadow the performance of GTC on the next generation supercomputer, Summit, a set of dedicated benchmarks have been executed on SummitDev and Titan, again employing the physics case used in Sect. 6.1. The scaling study of Sect. 6.2 was executed in May 2016, and since then much effort has been placed into GTC's GPU optimizations, such as removing unnecessary CPU to GPU data transfer and an increase in compiler support for texture, for use on Titan, and these additions have subsequently been ported for use on SummitDev. Hence, the speedups presented here are larger than those shown above.

Since SummitDev is a small prototype machine, 32 MPI processes were used per test. Tests covered both pure CPU runs and GPU dominant heterogeneous runs. Table 1 tabulates the results of 5 tests: 2 CPU runs, one on Titan and one on SummitDev, and 3 GPU runs, one on Titan and two on SummitDev. The CPU runs aimed to utilize both MPI and OpenMP parallelization with realistic job configurations, employing 8 OMP threads MPI rank on Titan and 5 OMP threads/MPI rank on SummitDev. This configuration leads to there being 2 ranks/CPU and 1 rank/CPU on SummitDev and Titan, respectively; hence, the SummitDev CPUs have a larger load in these runs, which explains why the SummitDev CPU timings are not as dramatically better than the Titan CPU timings. The GPU runs used 1 GPU/MPI rank and no OpenMP. Again, two GPU runs were carried out on SummitDev, each with a different library to solve the Poisson equation. One used PETSc, and the other used AmgX, the latter of which can take advantage of GPU acceleration. The Titan GPU run also uses

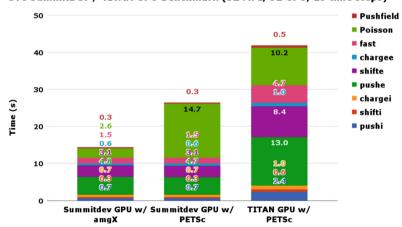

**Fig. 5.** The Phase II timing breakdown for GTC performance study on SummitDev and Titan for 15 time steps and 32 MPI processes.

<sup>&</sup>lt;sup>1</sup> The timings for the TITAN CPU w/PETSc case in Table 1 assume an ideal scaling in OMP threads from 8 threads to 16. i.e. the times presented in Table 1 for this case are those of the 8 OMP threads case, but they are divided by 2. The motivation for this is to set a lower bound in the possible GPU speedup attainable in TITAN.

PETSc to solve the Poisson equation. With AmgX, the total number of particles pushed per second on the SummitDev GPU run is  $1.29 \times 10^9$ .

The tabulated data is also presented in Fig. 4. The upper panel shows CPU only tests on both SummitDev and Titan for a range of OMP threads/MPI rank. The scaling from 8 to 16 OMP threads/MPI rank in Titan was poor. This is in part due to there being a decrease in efficiency when using OMP threads across cores on Titan—hence we assumed an ideal scaling from 8 to 16 OMP threads/MPI rank in Table 1 to obtain a lower bound in the possible speedup attainable. The lower panel presents the GPU timing data (Fig. 5).

Table 2 shows the GPU speedups obtained. SummitDev GPU speedups are relative to the SummitDev CPU case with 5 OMP threads/MPI rank, and Titan GPU speedups are relative to the Titan CPU case with ideal OMP scaling from 8 to 16 threads/MPI rank. The overall speedups were 34.0 and 18.6 on SummitDev, for the AmgX and PETSc libraries, respectively, and 7.9 on Titan. The most notable speedups came from the particle push and shift routines on SummitDev, with a roughly 36 and 82 times speed up for the ion push and shift, respectively; and a roughly 27 and 76 times speed up for the electron push and shift, respectively. The high speedup factors are to large degree enabled by the very effective use of texture cache as described earlier, as well as need to further optimize the OpenMP threading version for CPU. Moreover, the utilization of the AmgX library decreases the Poisson time by 5.5 times. It is noteworthy that the SummitDev/GPU/AmgX to Titan/PETSc performance ratio is about 3X, roughly in line with the 4X flop rate ratio and 3X memory bandwidth ratio of SummitDev vs. Titan GPUs.

# 6.4 Performance and Scalability on Summit

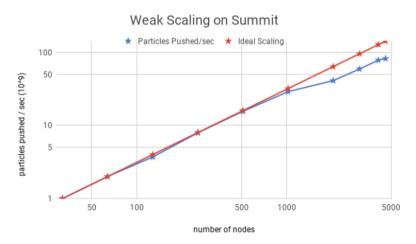

For testing the performance and scalability on Summit and the early science applications thereafter, a set of test problems was developed for evaluating performance. The physics simulation reported in [21] was prepared as a base case to measure improvements in performance. As shown in Table 3 and Fig. 6. GTC CPU-only runs scale almost perfectly up to 928 nodes (about 20% of the whole Summit) in the weak scaling test (i.e., by keeping constant number of particles per node). The simulation on 928 nodes uses  $2 \times 10^6$ , i.e., 1 million grids and  $2 \times 10^{11}$  particles utilizing 2/3 of the GPU memory. GTC simulations using all GPUs and CPUs also show good scaling, with a  $\sim 50\%$  efficiency at 928 Summit nodes when compared with the ideal scaling. The GTC speed up from CPU-only to GPU + CPU is over 20 at 928 Summit nodes, leading to an unprecedented speed of one trillion particle pushes in 2 s wall-clock time. Furthermore, GTC performance on each Summit GPU is about 8 times faster than each Titan GPU. Finally, as part of the Summit acceptance benchmark simulations, preliminary results of GTC running on 4576 Summit nodes (by Dr. Wayne Joubert of OLCF) show good scaling and similar performance, as shown in Fig. 7. The impressive GTC performance on Summit would enable integrated simulation of multiple physical processes.

Table 3. Wall-clock time for one trillion particle pushes in the GTC weak scaling test on Summit.

| Summit nodes | 16      | 64     | 256    | 512   | 928   |

|--------------|---------|--------|--------|-------|-------|

| GPU + CPU    | 58.43   | 15.37  | 4.99   | 2.92  | 2.00  |

| CPU only     | 2167.56 | 525.98 | 150.45 | 71.53 | 41.76 |

Fig. 6. Wall-clock time for one trillion particle pushes in the GTC weak scaling test on Summit.

**Fig. 7.** Phase-II weak scaling of GTC on Summit, with the number of nodes ranging from 32 nodes to 4576 nodes (almost the whole machine). Total particle number are increased by increasing the number of particles per node.

# 7 Conclusion

We have successfully restructured the current production version of gyrokinetic toroidal code (GTC) to a more modularized format with unified routines for all particle species, including thermal ions, thermal electrons, fast ions and fast electrons. This is followed by the optimizations using OpenACC directives to enable the GPU accelerations, which is also relatively friendly for fusion physics researchers and students. Other techniques have also been introduced to boost the performance to a higher level, which includes the binning technique where particle data storage is optimized for access. Hypre and Amgx have been adopted as alternatives to the PETSc field solver, which make the code benefit from the accelerations of many core CPUs (Hypre) and GPUs (AmgX).

Realistic profiles and parameters from fusion experiments have been used in GTC benchmarks to provide insights into technical interests and scientific significance. The strong and weak scaling studies have been performed and the overall speedup is about 2–3 times with a very good scalability on the whole Titan; and on SummitDev it shows an overall speedup of about 34 times. The real physics tests on Summit machine have also been conducted to tackle the self-consistent energetic particle physics in fusion plasmas, especially for ITER. These tests showed impressive scaling properties that reaches roughly 50% efficiency on 928 nodes which is 20% of total nodes of Summit. The GPU + CPU speed up from purely CPU is over 20 times, leading to an unprecedented speed.

Acknowledgments. The authors would like to thank Eduardo D'Azevedo for his many useful suggestions in the optimizations. This work was supported by the US Department of Energy (DOE) CAAR project, DOE SciDAC ISEP center, and National MCF Energy R&D Program under Grant Nos. 2018YFE0304100 and 2017YFE0301300, the National Natural Science Foundation of China under Grant Nos. 11675257, and the External Cooperation Program of Chinese Academy of Sciences under Grant No. 112111KYSB20160039. This research used resources of the Oak Ridge Leadership Computing Facility (OLCF) at the Oak Ridge National Laboratory, which is supported by the Office of Science of the U.S. Department of Energy under Contract No. DE-AC05-00OR22725.

## References

- 1. Lee, W.W.: Phys. Fluids 26, 556 (1983)

- 2. Lee, W.: J. Comput. Phys. 72, 243 (1987). ISSN 0021-9991

- 3. Littlejohn, R.G.: J. Plasma Phys. 29, 111 (1983)

- 4. Brizard, A., Hahm, T.: Rev. Mod. Phys. 79, 421 (2007)

- 5. Hahm, T.: Phys. Fluids (1958–1988) 31, 2670 (1988)

- 6. Frieman, E., Chen, L.: Phys. Fluids (1958–1988) 25, 502 (1982)

- 7. Rogister, A., Li, D.: Phys. Fluids B: Plasma Phys. (1989–1993) 4, 804 (1992)

- 8. Lin, Z., Chen, L.: Phys. Plasmas (1994-present) 8, 1447 (2001)

- 9. Lin, Y., Wang, X., Lin, Z., Chen, L.: Plasma Phys. Controlled Fusion 47, 657 (2005)

- 10. Holod, I., Zhang, W.L., Xiao, Y., Lin, Z.: Phys. Plasmas 16, 122307 (2009)

- 11. Liu, P., Zhang, W., Dong, C., Lin, J., Lin, Z., Cao, J.: Nucl. Fusion 57, 126011 (2017)

- 12. Lin, Z., Hahm, T.S., Lee, W.W., Tang, W.M., White, R.B.: Turbulent transport reduction by zonal flows: massively parallel simulations. Science **281**, 1835 (1998)

- 13. http://phoenix.ps.uci.edu/GTC

- 14. http://www.iter.org

- Lin, Z., Holod, I., Chen, L., Diamond, P.H., Hahm, T.S., Ethier, S.: Phys. Rev. Lett. 99, 265003 (2007)

- Xiao, Y., Lin, Z.: Turbulent transport of trapped electron modes in collisionless plasmas. Phys. Rev. Lett. 103, 085004 (2009)

- 17. Zhang, W., Lin, Z., Chen, L.: Phys. Rev. Lett. 101, 095001 (2008)

- Zhang, W., Decyk, V., Holod, I., Xiao, Y., Lin, Z., Chen, L.: Phys. Plasmas 17, 055902 (2010)

- 19. Zhang, W., Holod, I., Lin, Z., Xiao, Y.: Phys. Plasmas 19, 022507 (2012)

- 20. Zhang, C., Zhang, W., Lin, Z., Li, D.: Phys. Plasmas 20, 052501 (2013)

- 21. Wang, Z., et al.: Radial localization of toroidicity-induced alfven eigenmodes. Phys. Rev. Lett. **111**, 145003 (2013)

- 22. Cheng, J., et al.: Phys. Plasmas 23, 052504 (2016)

- 23. Kuley, A., et al.: Phys. Plasmas 22, 102515 (2015)

- 24. Peng, J., Zhihong, L., Holod, I., Chijie, X.: Plasma Sci. Technol 18, 126 (2016)

- 25. McClenaghan, J., Lin, Z., Holod, I., Deng, W., Wang, Z.: Phys. Plasmas 21, 122519 (2014)

- 26. Liu, D., Zhang, W., McClenaghan, J., Wang, J., Lin, Z.: Phys. Plasmas 21, 122520 (2014)

- 27. Lin, Z., Hahm, T.S., Ethier, S., Tang, W.M.: Size scaling of turbulent transport in magnetically confined plasmas. Phys. Rev. Lett. 88, 195004 (2002)

- Meng, X., et al.: Heterogeneous programming and optimization of gyrokinetic toroidal code and large-scale performance test on TH-1A. In: Kunkel, J.M., Ludwig, T., Meuer, H.W. (eds.) ISC 2013. LNCS, vol. 7905, pp. 81–96. Springer, Heidelberg (2013). https://doi.org/ 10.1007/978-3-642-38750-0

- 29. Wang, E., et al.: The gyrokinetic particle simulation of fusion plasmas on Tianhe-2 supercomputer. In: Workshop on Latest Advances in Scalable Algorithms for Large-Scale Systems (ScalA) 2016, International Conference for High Performance Computing, Networking, Storage and Analysis (SC2016), Salt Lake City, USA (2016)

- Madduri, K., et al.: Gyrokinetic toroidal simulations on leading multi- and manycore HPC systems. In: Proceedings of International Conference on High Performance Computing, Networking, Storage and Analysis, SC 2011 (2011)

- 31. Madduri, K., Im, E.J., Ibrahim, K.Z., Williams, S., Ethier, S., Oliker, L.: Gyrokinetic particle-in-cell optimization on emerging multi- and manycore platforms. Parallel Comput. **37**(9), 501–520 (2011)

- Wang, B., et al.: Kinetic turbulence simulations at extreme scale on leadership-class systems.

In: Proceedings of International Conference on High Performance Computing, Networking, Storage and Analysis, SC 2013, no. 82 (2013)

- 33. Ethier, S., Adams, M., Carter, J., Oliker, L.: Petascale parallelization of the gyrokinetic toroidal Code. LBNL Paper LBNL-4698 (2012)

- 34. Tang, W., Wang, B., Ethier, S.: Scientific discovery in fusion plasma turbulence simulations at extreme scale. Comput. Sci. Eng. 16, 44 (2014)

- 35. Dawson, J.M.: Rev. Mod. Phys. 55, 403 (1983)

- Birdsall, C.K., Langdon, A.B.: Plasma Physics via Computer Simulation. CRC Press, Boca Raton (2004)

- 37. Xiao, Y., Holod, I., Wang, Z., Lin, Z., Zhang, T.: Phys. Plasmas 22, 022516 (2015)

- 38. Feng, H., et al.: Development of finite element field solver in gyrokinetic toroidal code. Commun. Comput. Phys. 24, 655 (2018)

- 39. Ethier, S., Lin, Z.: Porting the 3D gyrokinetic particle-in-cell code GTC to the NEC SX-6 vector architecture: perspectives and challenges. Comput. Phys. Commun. **164**, 456–458 (2004)

- 40. White, R.B., Chance, M.S.: Phys. Fluids 27, 2455 (1984)

- 41. Joubert, W., et al.: Accelerated application development: the ORNL Titan experience. Comput. Electr. Eng. **46**, 123–138 (2015)

- 42. Vergara Larrea, V.G., et al.: Experiences evaluating functionality and performance of IBM POWER8+ systems. In: Kunkel, J.M., Yokota, R., Taufer, M., Shalf, J. (eds.) ISC High Performance 2017. LNCS, vol. 10524, pp. 254–274. Springer, Cham (2017). https://doi.org/10.1007/978-3-319-67630-2\_20

# Using Compiler Directives for Performance Portability in Scientific Computing: Kernels from Molecular Simulation

Ada Sedova<sup>(⊠)</sup>, Andreas F. Tillack, and Arnold Tharrington

Scientific Computing Group, National Center for Computational Sciences,

Oak Ridge National Laboratory, Oak Ridge, TN 37830, USA

{sedovaaa,tillackaf,arnoldt}@ornl.gov

**Abstract.** Achieving performance portability for high-performance computing (HPC) applications in scientific fields has become an increasingly important initiative due to large differences in emerging supercomputer architectures. Here we test some key kernels from molecular dynamics (MD) to determine whether the use of the OpenACC directivebased programming model when applied to these kernels can result in performance within an acceptable range for these types of programs in the HPC setting. We find that for easily parallelizable kernels, performance on the GPU remains within this range. On the CPU, OpenACCparallelized pairwise distance kernels would not meet the performance standards required, when using AMD Opteron "Interlagos" processors, but with IBM Power 9 processors, performance remains within an acceptable range for small batch sizes. These kernels provide a test for achieving performance portability with compiler directives for problems with memory-intensive components as are often found in scientific applications.

**Keywords:** Performance portability  $\cdot$  OpenACC  $\cdot$  Compiler directives  $\cdot$  Pairwise distance  $\cdot$  Molecular simulation

## 1 Introduction

Software development productivity is reduced when sections of high-performing programs must be frequently rewritten in low-level languages for new supercomputer architectures. This is not only a consequence of increased labor costs,

This manuscript has been authored by UT-Battelle, LLC under Contract No. DE-AC05-00OR22725 with the U.S. Department of Energy. The United States Government retains and the publisher, by accepting the article for publication, acknowledges that the United States Government retains a non-exclusive, paid-up, irrevocable, world-wide license to publish or reproduce the published form of this manuscript, or allow others to do so, for United States Government purposes. The Department of Energy will provide public access to these results of federally sponsored research in accordance with the DOE Public Access Plan (http://energy.gov/downloads/doe-public-access-plan).

<sup>©</sup> Springer Nature Switzerland AG 2019

S. Chandrasekaran et al. (Eds.): WACCPD 2018 Workshop, LNCS 11381, pp. 22–47, 2019. https://doi.org/10.1007/978-3-030-12274-4\_2

but also because the code can become more error-prone due to shortened lifetimes, multiple authors, and the inherent difficulty of programming close to machine-level [23,55,68,77]. Because of such considerations, creating performance portable applications has become an important effort in scientific computing [47,51], and is recognized as a significant software design goal by both the U.S. Department of Energy (DOE) [1,47,51] and the National Science Foundation (NSF) [15].

Classical molecular dynamics (MD) simulation is a popular tool for a number of fields within the physical and chemical sciences [30,69] and has been successfully implemented in the high-performance computing (HPC) setting by several developers [19,25,26,36,46,61,62,67,73]. The associated reports pay testimony to the extensive effort involved in porting these programs to different HPC platforms in order to meet increasingly rising standards. A variety of non-portable components are employed in leadership MD programs that allow for cutting-edge performance to be obtained. Some of the most performance-enhancing elements for per-node speedup include the CUDA C language (and CUDA API) for GPUbased acceleration, and architecture-specific SIMD intrinsic functions along with threading for the CPU portions [2-4, 19, 62, 66, 73]. CUDA C and the CUDA API, for example, are currently usable only with NVIDIA GPUs, so sections of code written in CUDA will have to be rewritten or translated for use on a different GPU-vendor's product; AMD GPUs, for instance, have recently been shown to be competitive to NVIDIA GPUs [35,75]. For optimal performance on CPUportions of heterogeneous architectures, architecture-specific SIMD instructions implemented with either intrinsic functions or vector instructions are often found to be essential in leadership MD programs [58]: without the use of SIMD, a majority of the processor's capacity may be unused by a program, and many compilers are not effective in auto-vectorizing code [40], but highly optimized SIMD instructions are architecture-specific and require a considerable effort. This amount of effort may not be optimal or even permissible for a domain scientist, as it will detract from time spent in scientific pursuits. Nevertheless, scientific computing needs can often be very niche-specific and thus commercial applications may not provide an adequate computational solution [57]. Modern science has advanced to a level that some amount of computing is required for both the theoretical and experimental branches: while computational science has become recognized as the "third pillar" of science by national agencies such as the NSF [13], current trends indicate that it is now essential to the functioning of the other two [76]. It is thus of great importance that scientific computing initiatives have accessible programming tools to produce efficient code that can be easily ported to a number of HPC architectures, and that the machine-level back ends are re-targeted and optimized by system or API developers, while maintaining a consistent, unified front-end interface for the computational scientist to use.

High level, compiler-directive based programing models such as OpenACC and OpenMP have the potential to be used as a tool to create more performance portable code [16,17]. Results of such attempts have been mixed,

however [28,31,47,48,51,56]. The creation of a dedicated portable program should provide the most optimal results [55,68]. Accordingly, here we test the possibility of creating a portable MD application starting with key kernels of the basic algorithm, and acceleration using OpenACC, to assess whether the resulting performance of these kernels is within an acceptable range to be used as part of HPC-based MD programs. This effort provides tests of the performance of OpenACC on kernels that involve non-negligible memory operations, and large memory transfers to the GPU, characteristic of many scientific applications. The kernels also represent calculations important to other types of computational work such as classification and data analysis.

# 2 Background

# 2.1 Performance Portability

To quantify portability, an index has been proposed, the degree of portability (DP):

$$DP = 1 - (C_P/C_R) \tag{1}$$

where  $C_P$  is the cost to port and  $C_R$  is the cost to rewrite the program [54]. Thus, a completely portable application has an index of one, and a positive index indicates that porting is more profitable. There are several types of portability; binary portability is the ability of the compiled code to run on a different machine, and source portability is the ability of the source code to be compiled on a different machine and then executed [54,55,68]. Here, costs can include development time and personnel compensations, as well as error production, reductions in efficiency or functionality, and even less tangible costs such as worker stress or loss of resources for other projects. For the HPC context, we can say that an application is performance portable if it is not only source-portable to a variety of HPC architectures using the Linux operating system and commonly provided compilers, but also that its performance remains in an acceptable range to be usable by domain scientists for competitive research. To avoid the ambiguity in the phrase "acceptable range," Pennycook and coworkers proposed the following metric for PP [45,60]:

$$PP(a, p, H) = \begin{cases} \frac{|H|}{\sum_{i \in H} \frac{1}{e_i(a, p)}} & \text{if } a \text{ is supported } \forall i \in H \\ 0 & \text{otherwise,} \end{cases}$$

(2)

where |H| is the cardinality of the set H of all systems used to test the application a, p are the parameters used in a, and  $e_i$  is the efficiency of the application on each system  $i \in H$ . Efficiency, here, can be the ratio of performance of the given application to either the best-observed performance, or the peak theoretical hardware performance [60].

Use of a high-level programming interface with a re-targetable back end that is standardized and supported by a number of both commercial and open-source initiatives has been found to be a critical element of portable application design [54,55]. OpenACC [16] was first developed to provide a high-level programming model for GPU programming, and now has been extended to multi-core machines. Conversely, OpenMP [17], once specific to CPU-based threading, has now been extended to the GPU. Both of these APIs offer compiler-directive-based interfaces with which to wrap sections of code for parallelization; they both appear in a similar format to the syntax used by OpenMP, which has now become familiar to many programmers of all levels. These two APIs are supported by a number of commercial hardware and compiler developers, and in addition, by the GNU project [18].

# 2.2 Molecular Dynamics

In molecular dynamics, a system, represented by atomistic units, is propagated in time based on some calculated forces using a numerical integration of Newton's equations of motion. The simulation cannot proceed with the next step until the previous one is completed; furthermore, a very small time-step is required to keep the simulation from sustaining unacceptable drifts in energy, as compared to experimental timescales that the simulation may be modeling [69]. Therefore, minimization of time per step is highly important. Several open-source, highly parallel classical MD programs exist that can scale to over thousands of nodes of a supercomputer and are heavily used internationally for molecular research. These programs are able to perform a time step in less than two milliseconds for systems of hundreds of thousands of atoms, or in seconds for systems of hundreds of millions of atoms [19,36,46,62,67,73].

The classical molecular dynamics algorithm involves three main components: the integration step, the calculation of bonded forces, of pairwise short-range non-bonded (SNF) forces, and the calculation of long-range forces. The integration step is generally the quickest part of the calculation, and as it has some memory-intensive aspects, is often calculated using the CPU, in implementations using heterogeneous architectures. The long-range forces calculation, in most implementations, involves an Ewald-sum, and requires Fourier transforms. The SNFs consist of the Lennard-Jones interaction, and short-range electrostatic forces. The Lennard-Jones interaction is an empirical function created to approximate the dispersive, or van der Waals forces, which in reality are purely quantum effects. The functional forms for these two additive forces are:

$$F_{LJ}(\mathbf{r_{ij}}) = \left[12\left(\frac{\sigma_{ij}^{12}}{r_{ij}^{13}}\right) - 6\left(\frac{\sigma_{ij}^{6}}{r_{ij}^{7}}\right)\right] \frac{\mathbf{r}_{ij}}{r_{ij}},\tag{3}$$

$$F_C(\mathbf{r_{ij}}) = \frac{1}{4\pi\epsilon_0} \frac{q_i q_j}{r_{ij}^2} \frac{\mathbf{r}_{ij}}{r_{ij}}.$$

(4)

Here  $F_{LJ}(\mathbf{r_{ij}})$  is the Lennard-Jones force on atom i due to atom j, with  $\mathbf{r_{ij}}$  being the vector connecting atom i to atom j.  $\sigma$  is a parameter that depends on the atom type of both interacting atoms, and  $F_C(\mathbf{r_{ij}})$  is the analogous Coulomb force, with  $q_n$  being the point-charge value assigned to atom n, and  $\epsilon_0$  the permittivity of free space; both are functions of the inter-atomic distance [5,69].

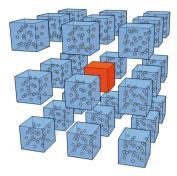

Fig. 1. Schematic of the interaction neighbors for cell-cell interactions involved in the spatial decomposition in the molecular dynamics algorithm. The central box (orange), interacts with itself, and with its 26 immediate neighbors, creating a total of 27 interactions for each cell in the grid, if in a periodic system, or a range of interactions from 8–27 if in a non-periodic system. Boxes are exploded outward for visualization purposes, but sides are touching in the actual grid. (Color figure online)

The Lennard-Jones and short-range electrostatic forces rapidly decay to zero outside of a radius of about 10–14 angstroms. This creates an excellent mechanism for reducing the total calculation by imposing a distance-based radial cutoff on each atom, outside of which no interactions are considered. Algorithmically, the SNF calculation usually consists of a spatial decomposition, or domain

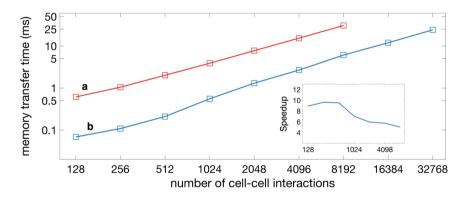

Fig. 2. Sparsity plot of distance matrix of all cell-cell distances, with all distances outside of radial cut-off of 10 angstroms set to zeros (and colored white), for a solvated system of 30,000 atoms (small protein), and all distances within the cut-off in blue. The number of cells in each direction is 6, resulting in a total of 46,656 cell-cell distances. 4096 of these are actually calculated in a non-periodic MD simulation due to the cut-off scheme. (Color figure online)

decomposition, of the system, into a three-dimensional grid of cells, followed by a binning of the atoms into their associated cells with some sort of sorting procedure. After this the pairwise forces on each atom can be calculated and summed [58,65]. These forces, as can be seen from their equations, depend on the pairwise distances between an atom and all other atoms within the radial cut-off. If the spatial decomposition is performed so that the cells' dimensions are close to the LJ cut-off distance, then only the interacting cell-cell pairs need to be searched for interacting atoms, for each cell [65]. In the periodic regime, all cells have 26 neighbors, and distances of all atoms within the central cell must be calculated as well, resulting in 27 cell-cell interactions that must be calculated for each cell in the grid of the domain decomposition. Figure 1 shows a central cell and its interacting cell neighbors. Figure 2 shows a sparsity plot of the distance matrix for all cell-cell interactions in the system, with those having distances greater than the cut-off set to zero and colored white, and interacting cells colored blue. As can be seen, the cut-off creates a banded structure to the matrix, and reduces the number of cell-cell calculations by about 90%.

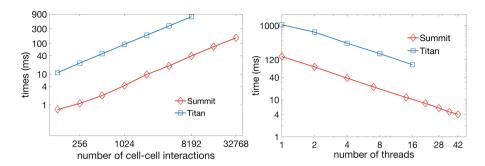

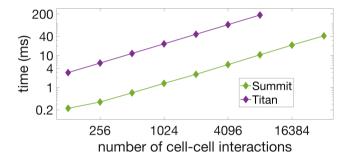

# 3 Portability Goals: Timings and Architectures

HPC MD developers have continuously pushed for increasingly shorter per-time-step execution rates. Currently, GROMACS [19] and NAMD [73] exhibit highly competitive timings per time-step. For 21 M atoms, NAMD attained about 5 ms per time-step and for a 224 M atom system, about 40 ms per time-step using 4096 nodes, according to published benchmarks [6,63]. In 2015 GROMACS reported a sub-millisecond time-step for a 80,000 atom system using only 32 nodes, with Intel E5-2680v2 processors with 20 CPU cores and 2 K20X NVIDIA GPUs, and 1.7 ms per step for a 2 M atom system using 512 nodes of the same processor type but without GPU [46]; thus performance on a multi-core machine can actually exceed that of a GPU-enabled supercomputer for MD. Using GROMACS 5.1.3 on OLCF Titan, a Cray XK7 with AMD Interlagos CPUs and one NVIDIA K20X GPU per node we obtained a 1.2 ms time-step for a 1.1 M atom system using 1024 nodes. This level of performance has been attained and is expected on many-core, multi-core, and GPU-containing HPC systems.

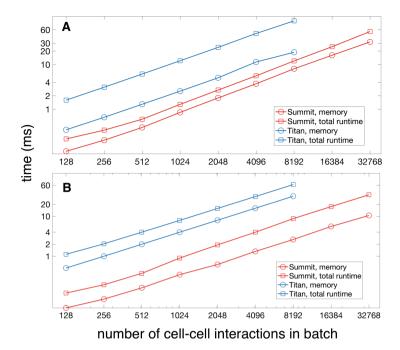

We test some key kernels from a MD calculation to see if parallelization with OpenACC can be performed while remaining under 7 ms/time-step for a system under 20 M atoms, or 55 ms/time-step for a system of about 220 M atoms, after domain decomposition. On a single node, the total times for the kernels must be well below these numbers while at the same time the job size on the node must be large enough so that the total domain decomposition would not use more that about 2000 nodes for a smaller system, and 4000 nodes for a larger system. Common domain decomposition for MD programs involves computing the SNFs acting on about 15 K atoms on a single node. For around 15 K atoms, there are about 3,000 cell-cell interactions, so what we aim for is a total kernel time under 6 ms for about 3,000 cell-cell interactions, or 50 ms for about 12,000 cell-cell interactions, which leaves time for communication and other less time-consuming portions of the calculation, and corresponds to an 80% efficiency score

compared to NAMD, and if maintained for all architectures tested, would result in a minimum of 80% performance portability score in (2). We test whether this performance can be maintained using the same source code, on nodes with multi-core CPUs and on heterogeneous nodes containing a GPU.

### 4 Designing the Kernels

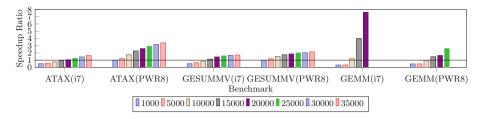

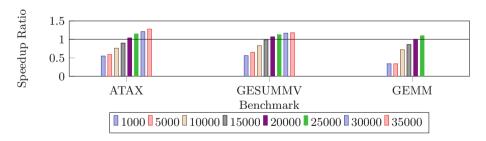

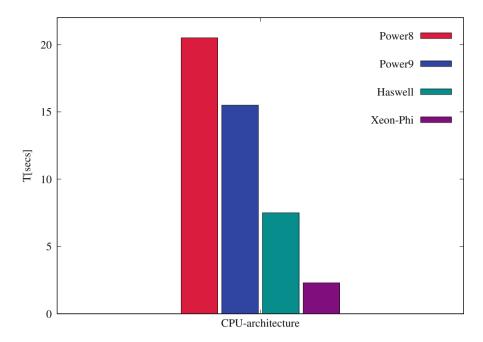

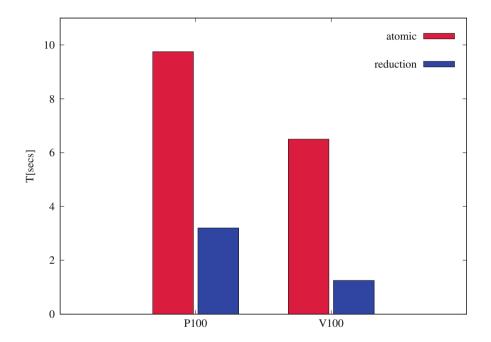

#### 4.1 The Programming Model and Its Portable Subset